## **Senior Design 1**

## Frequency Resolved Electrical Gating Device to Measure Ultrashort Optical Pulses

# College of Electrical Engineering and Computer Science College of Optics and Photonics

University of Central Florida Dr. ChungYong Chan Dr. Aravinda Kar

## Group 2 CREOL

Namisha Jagmohan - Photonic Science & Engineering, Electrical Engineering

Odane Lennox - Electrical Engineering

Keana Paredes - Photonic Science and Engineering

Alex Wheat – Computer Engineering

Project Advisor: Andrea Blanco-Redondo

Project Committee: Andrea Blanco-Redondo, Nazanin Rahnavard, Avra Kundu

## **Contents**

| Chapter 1 Executive Summary                                       | 1  |

|-------------------------------------------------------------------|----|

| Chapter 2 Project Description                                     | 1  |

| 2.1 Motivation                                                    | 1  |

| 2.2 Background                                                    | 2  |

| 2.3 Project Goals                                                 | 7  |

| 2.3.1 Basic Goals                                                 | 7  |

| 2.3.2 Advanced Goals                                              | 7  |

| 2.3.3 Stretch Goals                                               | 8  |

| 2.4 Objectives                                                    | 8  |

| 2.5 Engineering Specifications                                    | 10 |

| 2.6 Block Diagrams                                                | 10 |

| 2.6.1 Hardware Block Diagram                                      | 10 |

| 2.6.2 Electronics Block Diagram                                   | 12 |

| 2.6.3 Software Block Diagram                                      | 13 |

| 2.7 House of Quality                                              | 14 |

| 2.7.1 House of Quality Description                                | 14 |

| Chapter 3 Research                                                | 15 |

| 3.1 Existing Similar Projects, Products and Relevant Technologies | 15 |

| 3.1.1 FROG                                                        | 15 |

| 3.1.2 TADPOLE                                                     | 15 |

| 3.1.3 SEA TADPOLE                                                 | 16 |

| 3.1.4 SPIDER                                                      | 16 |

| 3.1.5 FREG First Configuration                                    | 17 |

| 3.2 Hardware Part Selection                                       | 17 |

| 3.2.1 FREG Components                                             | 17 |

| 3.2.2 Optical Spectrum Analyzer                                   | 35 |

| 3.2.3 PCB                                                         | 42 |

| 3.3 Software Part Selection                                       | 62 |

| 3.3.1 Programming Language Archetype                              | 62 |

| 3.3.2 Programming Language                                        | 63 |

| 3.3.3 Deconvolution Algorithm                                     | 65 |

| 3.3.4 PCB CAD Software                                            | 67 |

| 3.3.5 SPICE Software                                                     | 68 |

|--------------------------------------------------------------------------|----|

| 3.3.6 Housing CAD Software                                               | 69 |

| 3.3.6 MCU Communication Protocol                                         | 71 |

| Chapter 4 Standards and Design Constraints                               | 73 |

| 4.1 Standards                                                            | 73 |

| 4.1.1 IEEE-370-2020                                                      | 73 |

| 4.1.2 IEEE 2999-2023                                                     | 74 |

| 4.1.3 IEEE 287-2007                                                      | 75 |

| 4.1.4 ANSI Z136.1 (2022)                                                 | 75 |

| 4.1.5 ANSI Z136.8                                                        | 76 |

| 4.1.6 IEC 62129-1 (2016-01)                                              | 76 |

| 4.1.7 IEC 60529 (1989 + A1: 1999 + A2: 2013)                             | 77 |

| 4.1.8 IPC-2221                                                           | 77 |

| 4.1.8 IPC-4101                                                           | 78 |

| 4.2 Constraints                                                          | 78 |

| 4.2.1 Optical Constraints                                                | 78 |

| 4.2.2 Hardware Constraints                                               | 79 |

| 4.2.3 Software Constraints                                               | 80 |

| 4.2.4 Safety Constraints                                                 | 81 |

| 4.2.5 Time Constraints                                                   | 82 |

| 4.2.6 Economic Constraints                                               | 82 |

| Chapter 5 Comparison of ChatGPT with LLMs                                | 83 |

| 5.1 Pros, Cons, and Limitations of LLMs                                  | 83 |

| 5.1.1 ChatGPT                                                            | 83 |

| 5.1.2 New Bing                                                           | 84 |

| 5.1.3 Bard                                                               | 84 |

| 5.1.4 Comparison of LLM Chatbots                                         | 85 |

| 5.2 Effects on Senior Design                                             | 86 |

| 5.2.1 Benefits and Detriments of Information Access through LLMs         | 86 |

| 5.2.2 Benefits and Detriments of Text Content Generation by LLMs         | 87 |

| 5.2.3 Benefits and Detriments of Image Generation and Analysis by LLMs . | 87 |

| Chapter 6 Hardware Design                                                | 88 |

| 6.1 FREG Design                                                          | 88 |

| 6.2 Optical Spectrum Analyzer Design                                     | 90 |

| 6.2.1 Optical Spectrum Analyzer Calculations            | 90  |

|---------------------------------------------------------|-----|

| 6.2.2 Optical Spectrum Analyzer Simulation in Zemax     | 93  |

| Chapter 7 Software Design                               | 96  |

| 7.1 Embedded Systems Software                           | 96  |

| 7.1.1 Embedded Software Flowchart                       | 97  |

| 7.1.2 Time-Delay Line and Computer Communication (UART) | 97  |

| 7.1.3 Motor Control                                     | 99  |

| 7.2 PC (MATLAB) Software                                | 99  |

| 7.2.2 Spectrogram Assembly                              | 100 |

| 7.2.3 FREG Algorithm                                    | 101 |

| 7.2.4 User Interface                                    | 102 |

| Chapter 8 System Fabrication and Prototype Construction | 103 |

| 8.1 PCB Layout                                          | 103 |

| 8.2 Housing                                             | 110 |

| Chapter 9 System Testing                                | 114 |

| 9.1 Optical Hardware Testing                            | 114 |

| 9.2 Electrical Hardware Testing                         | 116 |

| 9.3 Software Testing                                    | 116 |

| 9.3.1 Embedded Software                                 | 116 |

| 9.3.2 MATLAB Software                                   | 117 |

| 9.3.3 MultisimLive Software                             | 117 |

| 9.4 Plan for Senior Design 2                            | 117 |

| Chapter 10 Administration                               | 118 |

| 10.1 Budget Estimates                                   | 118 |

| 10.2 Milestones                                         | 119 |

| 10.3 Work Distribution                                  | 120 |

| 10.4 LLM Declaration                                    | 120 |

| Chapter 11 Conclusion                                   | 121 |

| Appendix A                                              | 123 |

# **Table of Figures**

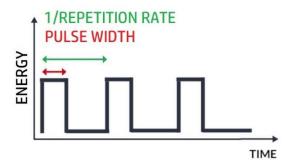

| Figure 1: Optical Pulse Train. Shows a pulse train and relevant attributes such as the repetition rate, pulse width, and pulse energy. The periodic nature of the input pulse train is vita to the FREG's ability to retrieve the pulse amplitude and phase                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

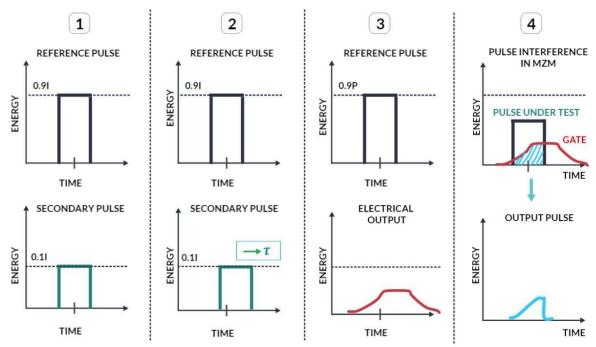

| Figure 2: FREG Snapshots. Shows "snapshots" of the signals through the reference arm and secondary arm at different locations in the system. We can see the transformation of the secondary pulse and its subsequent recombination with the reference pulse.                                                                                               |

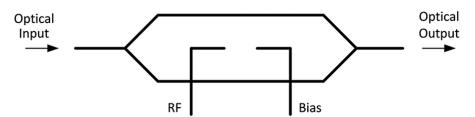

| Figure 3: MZM Structure. Shows a basic top-view representation of an MZM. The optical input is split into two arms, one of which is under a DC bias and is driven by an input RF signal. When the signals are recombined at the Y-junction, any differences in phase as well as how much the pulses are overlapped will determine the amplitude modulation |

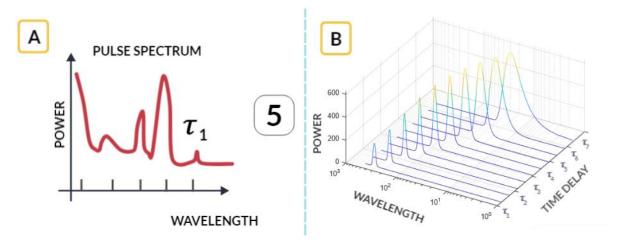

| Figure 4a (Left): 2D Spectrum Example. Shows an example of what a pulse spectrum would look like. This is necessary for reference in conjunction with Figure 4b, as this shows how the spectrums are compiled to create a spectrogram.                                                                                                                     |

| Figure 4b (Right): 3D Spectrogram Example. Shows an example of what the spectrogram would look in 3-D, rather than the 2-D representation (such as Figure 4a). We see that each of the output spectrums created by varying the time delay are compiled to create a spectrogram                                                                             |

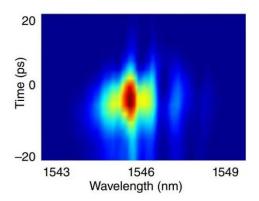

| Figure 5a: 2D Spectrogram Example. Shows an example of a 2D spectrogram. These spectrograms will be the output from the spectrum analyzer and the input into the deconvolution algorithm. [3]                                                                                                                                                              |

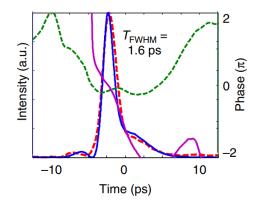

| Figure 5b: Retrieved Pulse Phase and Amplitude. Shows an example of the retrieved pulse and phase information from a spectrogram. Ideally, our GUI will return a similar result. The dashed red line shows the measured intensity, dashed green shows the measured phase, and the magenta and blue are the respective modelled values. [3]                 |

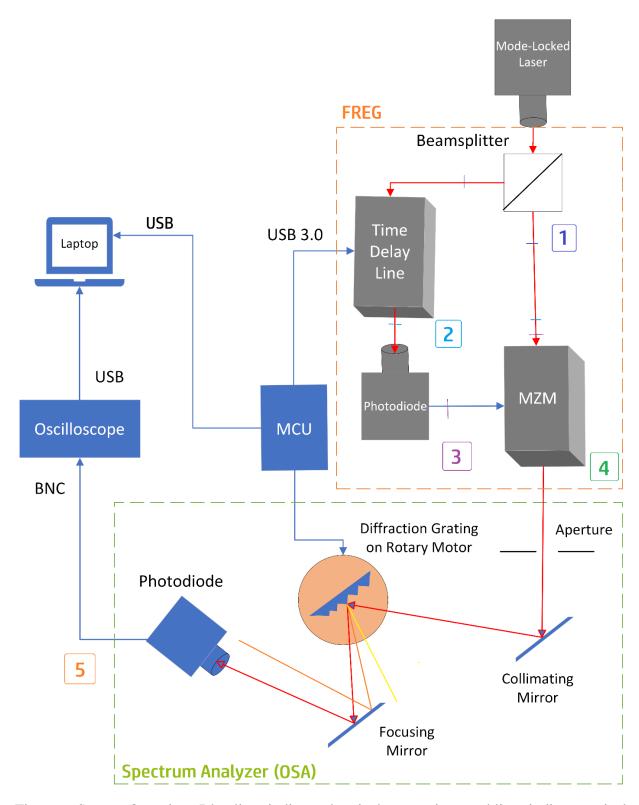

| Figure 6: System Overview. Blue lines indicate electrical connections; red lines indicate optical signals.                                                                                                                                                                                                                                                 |

| Figure 7: Overall Block Diagram                                                                                                                                                                                                                                                                                                                            |

| Figure 8: Electronics Block Diagram                                                                                                                                                                                                                                                                                                                        |

| Figure 9: Software Block Diagram.                                                                                                                                                                                                                                                                                                                          |

| Figure 10: House of Quality for the FREG device                                                                                                                                                                                                                                                                                                            |

| Figure 11: MZM Crystal Cuts. Shows the differences between the different single-drive MZM crystal-cut configurations. [17]                                                                                                                                                                                                                                 |

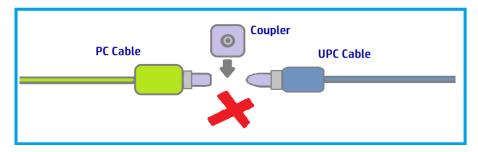

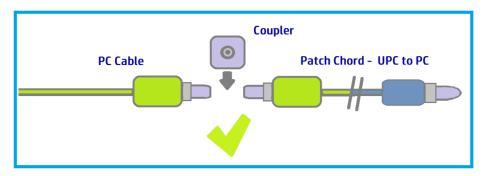

| Figure 12A: Shows the proper connectorization of fiber to minimize back reflections and insertion loss. Fig. 12A demonstrates that the coupler cannot be used because the PC cable does not match the patch cord                                                                                                                                           |

| Fig. 12B correctly shows the fiber ends must be the same to use the coupler properly 23                                                                                                                                                                                                                                                                    |

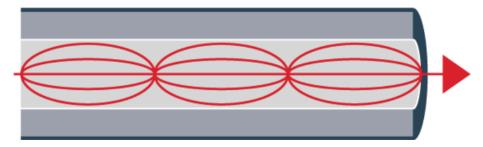

| Figure 13: Graded Index Fiber with light propagating from core to edge of cladding 31                                                                                                                                                                                                                                                                      |

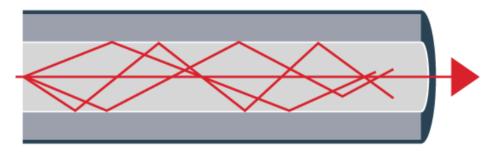

| Figure 14: Step Index Fiber with light traveling in zigzag due to light arriving at differen                                                                                                                                                                                                                                                               |

| times 32                                                                                                                                                                                                                                                                                                                                                   |

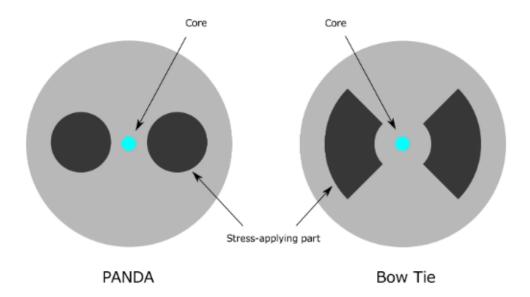

| Figure 15: Schematic of two different types of PM fibers. The PANDA on the left side will be the structure of the MZM fiber input, which is different from the Bow Tie structure on the right                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| side                                                                                                                                                                                                                                                                                                    |

| Figure 16: PANDA PM fiber for our Mach Zender Modulator                                                                                                                                                                                                                                                 |

| (Left) Equation which relates the energy of a photon to its wavelength. (Right) Equation which describes the standing wave condition of a resonant cavity.                                                                                                                                              |

| Figure 17: Example of Diffraction Grating Dispersion. Shows the dispersion of lighthrough a diffraction grating, utilizing the conceptual understanding of multiple-slit interference [69]                                                                                                              |

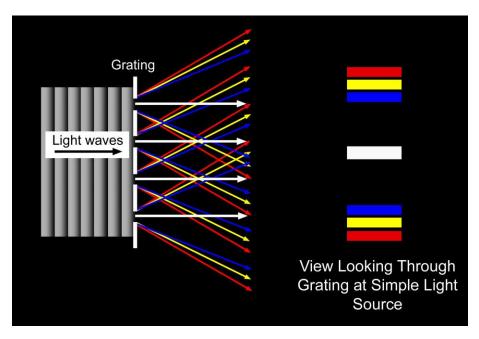

| Figure 18: USB-to-UART Bridge Interface                                                                                                                                                                                                                                                                 |

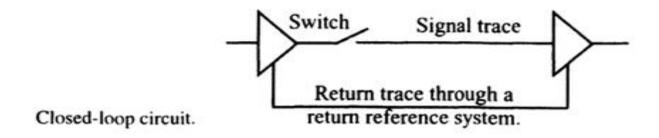

| Figure 19: Closed-loop Circuit                                                                                                                                                                                                                                                                          |

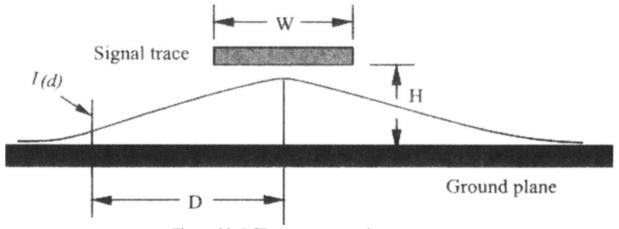

| Figure 20: PCB Routing Topology                                                                                                                                                                                                                                                                         |

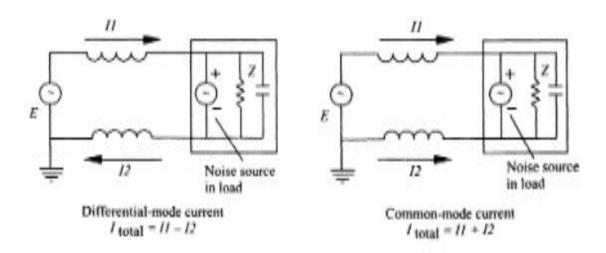

| Figure 21: Common- and differential-mode current                                                                                                                                                                                                                                                        |

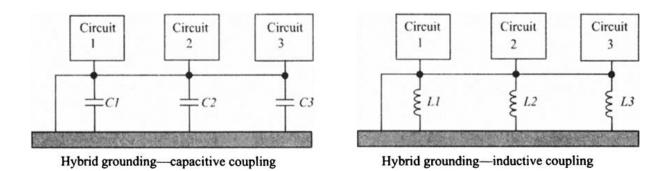

| Figure 23: Hybrid grounding methodologies                                                                                                                                                                                                                                                               |

| Figure 24: Series resonant circuit                                                                                                                                                                                                                                                                      |

| Table 26: This comparison table lists the three separate CAD programs that could be used throughout the duration of the project. The listed specifications comparison is just to show what each program has to offer.                                                                                   |

| Figure 25: Qualitatively shows how the desired wavelength range is spread across the detector                                                                                                                                                                                                           |

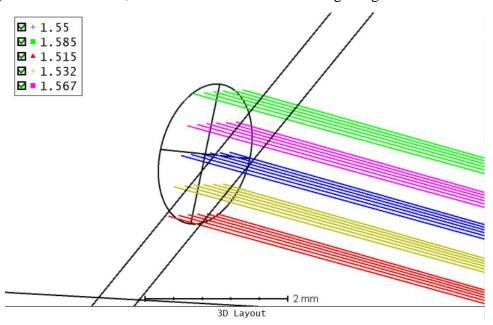

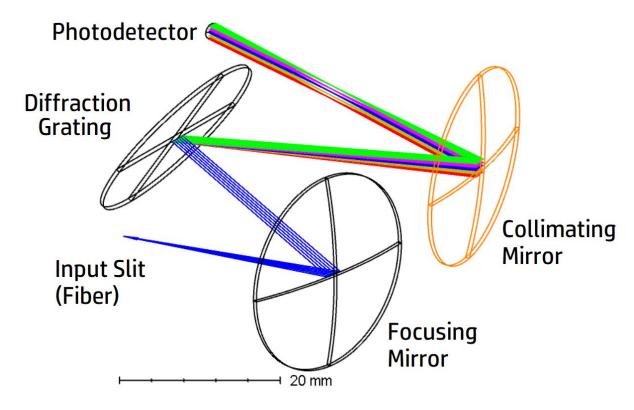

| Figure 26: Shows the simulated slit image on the detector, which is the imaging plane. We see that the total region shown is 4000 microns or 4 mm. Thus, every box is 0.4 mm. Because the wavelength range spans ~6 boxes, we have calculated the wavelength range to span 2.4 mm of the imaging plane. |

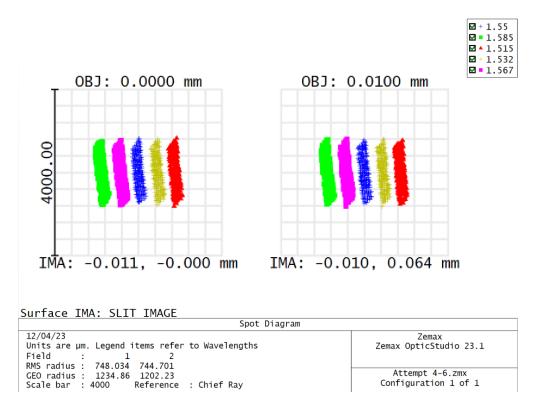

| Figure 27: Shows the overall spectrum analyzer design in Zemax, in its current iteration                                                                                                                                                                                                                |

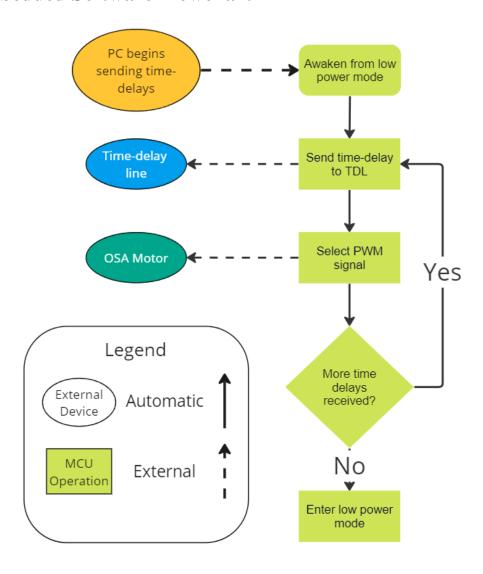

| Figure 28: Embedded software flowchart                                                                                                                                                                                                                                                                  |

| Figure 29: PC software flowchart showing the operation of the code                                                                                                                                                                                                                                      |

| Figure 30: Mock UI diagram for the computer program                                                                                                                                                                                                                                                     |

| Figure 36: PC USB-to-UART Bridge                                                                                                                                                                                                                                                                        |

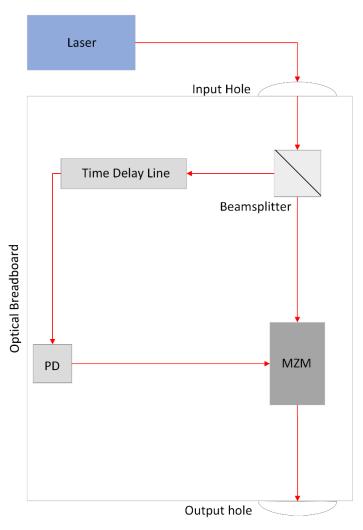

| Figure 37: First Housing design to only focus on the FREG system. The enclosure would have a lid to make the enclosure more discrete while the sides of the housing will just have two holes for the input and output beam                                                                              |

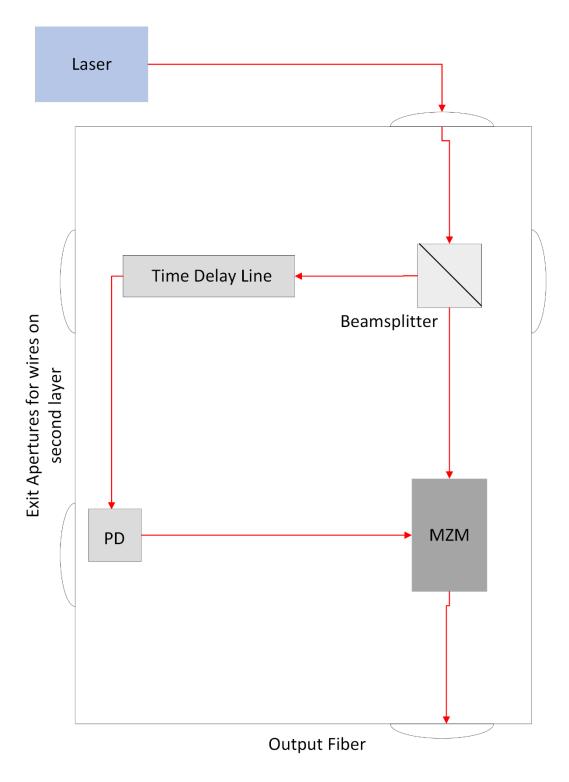

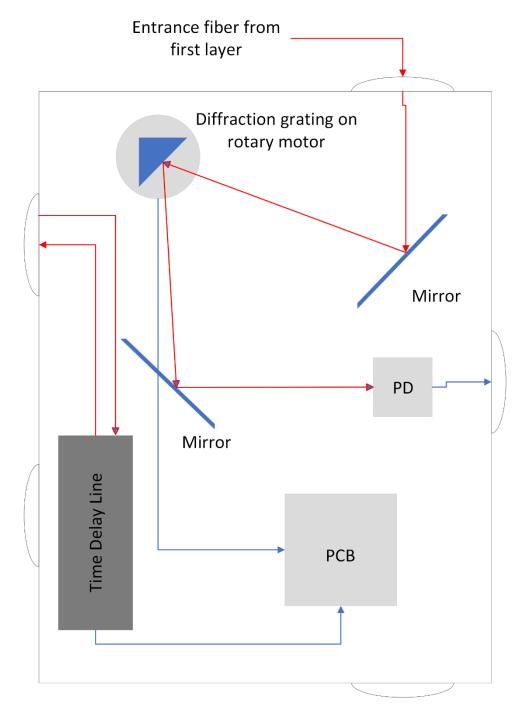

| Figure 39: This is the Second layer of the enclosure that will hold the time delay line, OSA and the electrical components.                                                                                                                                                                             |

| Figure 40: Shows the testing data done for characterizing the beamsplitter. The "Blue refers to the arm which 90% of the power is split into, the "Red" refers to the arm where 10% of the power is split into.                                                                                         |

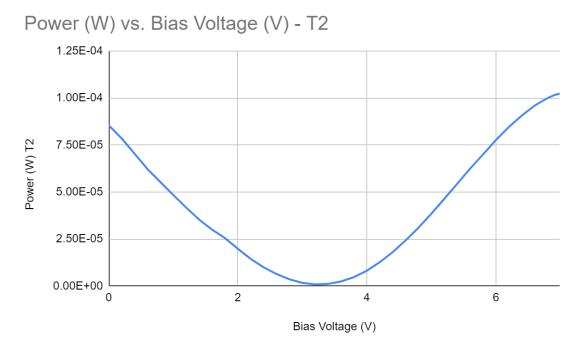

| Figure 41: Shows an example of the modulator biasing curve obtained from testing. | This |

|-----------------------------------------------------------------------------------|------|

| was obtained for a JDSU 10 GHz MZM.                                               | 115  |

| Figure 42: Milestones Chart                                                       | 120  |

## **Index of Tables**

|        | Table 1: Engineering Specifications                                                                        | 10  |

|--------|------------------------------------------------------------------------------------------------------------|-----|

| Lithiu | Table 2: Pockel's Effect or Linear Electro-Optic Coefficients and Refractive Indices m Niobate at 1550 nm. |     |

|        | Table 3: Comparison of Mach-Zender Modulators                                                              | 24  |

|        | Table 4: Comparison of Photodiodes                                                                         | 27  |

|        | Table 5: Comparison of Time-Delay Lines                                                                    | 28  |

|        | Table 6: Comparison of Reflective Diffraction Gratings                                                     | 39  |

|        | Table 7: Photodiodes for the FREG                                                                          | 40  |

|        | Table 8: Comparison of Rotary Motors                                                                       | 42  |

|        | Table 9: Interface controller connection                                                                   | 52  |

|        | Table 10: USB-To-UART Interface                                                                            | 53  |

|        | Table 11: Microcontrollers                                                                                 | 53  |

|        | Table 12: Linear, Low Drop Out (LDO) Voltage regulator                                                     | 55  |

|        | Table 13: Switching Voltage regulator                                                                      | 56  |

|        | Table 14: Power O-Ring                                                                                     | 56  |

|        | Table 15: Comparison of External Successive-Approximation Resister (SAR) ADC                               | 57  |

|        | Table 16: Delta-Sigma ADC                                                                                  | 58  |

|        | Table 17: Dual Slope ADC                                                                                   | 58  |

|        | Table 18: Pipeline ADC                                                                                     | 59  |

|        | Table 19: Flash ADC                                                                                        | 59  |

|        | Table 20: PWM Controller                                                                                   | 61  |

|        | Table 21: Comparison of Programming Language Archetypes                                                    | 63  |

|        | Table 22: Comparison of Programming Languages                                                              | 64  |

|        | Table 23: Comparison of Deconvolution Algorithms                                                           | 66  |

|        | Table 24: Comparison of PCB CAD Software                                                                   | 68  |

|        | Table 25: Comparison of SPICE Software                                                                     | 69  |

|        | Table 26: Comparison of CAD programs                                                                       | 71  |

|        | Table 27: Comparison of MCU communication protocols                                                        | 72  |

|        | Table 28: Survey of Femtosecond Lasers                                                                     | 91  |

|        | Table 29: Lens Data Editor (Post-Optimization)                                                             | 94  |

|        | Table 30: Tilt of Various Optical Components in the Spectrometer Design                                    | 95  |

|        | Table 32: Budget Estimates                                                                                 | 118 |

|        | Table 33: Work Distribution                                                                                | 120 |

## **Chapter 1 Executive Summary**

The proposed project is an apparatus for the characterization of ultra-short, low energy optical pulse trains to measure their pulse amplitude and phase. This apparatus is necessary as ultra-short optical pulses, specifically those on the order of a few picoseconds in duration, cannot be measured by typical photodetectors alone. This is due to limits in photodetector electrical response times with respect to electron transit time and inherent capacitances and resistances within the device circuitry. Additionally, the optical pulses we are interested in characterizing are low energy (<40 pJ); Because of this, we cannot use well-established means, such as Frequency-Resolved Optical Gating (FROG), to retrieve the pulse amplitude and phase. Thus, to circumvent the limits of electronic circuitry and detect these low-energy pulses, we aim to build a FREG (Frequency-Resolved Electrical Gating) system.

The FREG requires supporting hardware and software to function independently, namely an optical spectrum analyzer, a blind deconvolution algorithm, and a custom PCB. The spectrum analyzer allows us to build a spectrogram from the output optical signals of the FREG. The blind deconvolution algorithm then takes that spectrogram and deconvolves it so we can retrieve the pulse information. The microcontroller on the PCB handles communications between the FREG, spectrum analyzer, and the computer. The design of these sub-systems will also be detailed in this paper.

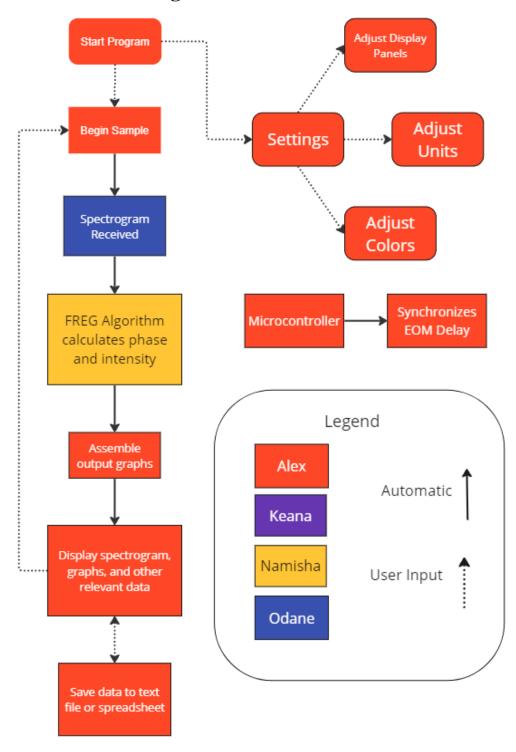

The software used in the system has 2 distinct portions: embedded software which controls the microcontroller and a computer program which the user interacts with. The embedded software handles the FREG hardware by communicating the necessary data between components as well as directly controlling other components. The computer program allows the user to begin the pulse retrieval process and view the results of the retrieval. This involves first acquiring data from the FREG hardware and assembling it into a usable format. The deconvolution is then performed using complex math, and the characterization data is displayed to the user as the results of the process.

A Multi-layer PCB integration will be incorporated into the FREG system to ensure proper power distribution and establishment of various communications links. The time delay line and the PC consist of a USB 2.0 port connection to the Microcontroller. Implementing a USB-to-UART bridge converter is important for relaying and receiving data for both interfaces. The precision motor is the third major aspect of the system that requires incorporating a designed PWM controller to send instructions from the MCU based on the data received by the time delay line. Design techniques for lowering the impedance of the board will be included as the PCB contains high-speed components which can lead to malfunctions and faults in the routing of the traces if ignored. Calculations and comparisons on different components will be carefully analyzed to determine the optimal circuit designs necessary to meet all parameters of the FREG system without compromising on performance.

## **Chapter 2 Project Description**

#### 2.1 Motivation

The motivation for ultra-short, low-energy optical pulses in these devices is due to their use in the telecommunications domain. Ultra-short optical pulses are necessary for pushing bit rates higher, as the shorter the pulses are, the more bits can be transmitted per second. This is

important as data throughout needs increase exponentially with each year. Additionally, these optical pulses for communications are low energy, on the order of picojoules to femtojoules, and are thus low-power pulses ( $\sim 10~\mu W$ ) when factoring in their short durations. This aspect is important for the sake of power efficiency in these telecommunication systems.

Thus overall, the FREG apparatus accomplishes two goals for the customer: It returns the amplitude of a pulse, as well as its phase. These attributes of the pulse are necessary to retrieve, as knowing these properties helps us counteract dispersion of the pulses as they propagate through the systems they will be implemented into. Measuring amplitude is important for achieving the desired high data transmission rates. This is because pulse amplitude also tells us about its duration. The relevance of the phase of these optical pulses is that it is needed for mitigating signal degradation due to intramodal dispersion. [1]

#### 2.2 Background

The FREG is a successor to the more commonly known FROG (Frequency-Resolved Optical Gating) system. However, the FROG setup is unideal for our application due to its need for nonlinear optical pulse mixing, which requires high-energy pulses. The FREG's desired application will mainly be for the characterization of optical pulse outputs from fiber lasers and photonic crystal waveguides which will be outputting low-energy optical pulses. The FREG's ability to resolve ultra-short pulses without the need for non-linear optical pulse mixing makes the system much more sensitive compared to FROG, to the extent that it is able to accurately measure pulses which contain less than 100 photons. [2]

The primary concept of the FREG is taking advantage of convolution theory to make a difficult measurement in the time-domain obtainable. This is done via pulse interference, signal conversion to the frequency domain, and a subsequent deconvolution algorithm to extract pulse duration and phase. The system utilizes signal gating to create a 2D spectrogram of the device-under-test's (DUT's) impulse response behavior. The input signal with a varying time delay is what we call the "gating" function, as the amount of delay determines the pulse-overlap and subsequent intensity modulation in the FREG output.

We will now discuss the overall system set-up. We begin with the input. As seen in Figure 1, the input we will be testing the FREG system with is a mode-locked laser. There may be other inputs, depending on what the user would like to characterize. A mode-locked laser outputs short optical pulses in the time domain, which are often referred to as a pulse train. This output light is not continuously flowing (or continuous wave), but instead switches on and off. These optical pulses have a consistent amplitude and phase which we are interested in retrieving. The pulse amplitude will tell us the width of the pulse as well. The repetition rate of a laser is how many pulses are emitted per second. The inverse of the repetition rate tells us the period of the laser output, or the pulse-to-pulse duration. This information is described in Figure 1.

Figure 1: Optical Pulse Train. Shows a pulse train and relevant attributes such as the repetition rate, pulse width, and pulse energy. The periodic nature of the input pulse train is vital to the FREG's ability to retrieve the pulse amplitude and phase.

For the sake of simplicity, we are going to look at a singular pulse in this pulse train for our analysis through the FREG. This assumption does not impact any analyses of the FREG functionality, because of the periodic nature of the signals being used. We can also make this assumption because the pulse width will generally be much smaller than the inverse of the repetition rate (i.e. the pulse-to-pulse duration). For the following explanation of the device's operation, we will be referring to Figure 2 in conjunction with Figures 4a and 4b. There is numbering on the figures to keep track of important locations.

The optical signal/pulse first propagates into the system. When it reaches the beamsplitter, the optical energy is split into a given ratio, dependent on the beam splitter which is chosen. For the purposes of this explanation, we will assume that it transmits 90% of the light into the reference arm and 10% of the light into the secondary arm. After this beamsplitter is position 1 defined on Figures 2 and 6. We see that there are two pulses, with different fractions of the incident power.

Figure 2: FREG Snapshots. Shows "snapshots" of the signals through the reference arm and secondary arm at different locations in the system. We can see the transformation of the secondary pulse and its subsequent recombination with the reference pulse.

The pulses continue propagating. For clarity, the entire system is connectorized via optical fiber, it is not free-space propagating, as this would introduce more losses and noise. The reference pulse continues propagating through fiber and experiences no changes. The secondary pulse however, encounters the variable time delay line. This component introduces a change in the optical path length within the secondary arm. This delay line is adjustable. Thus, the secondary pulse is shown to be delayed in time with respect to the original pulse at point 2, because the secondary pulse had to travel an extended distance.

We then reach point 3, where the propagation of the secondary signal gets more complicated. The reference signal remains the same, still propagating through the fiber. The secondary signal encounters a fast photodiode, where the optical signal is converted to an electrical signal. These optical pulses are on the femtosecond scale, which far exceeds the electrical bandwidth of the photodiode. This means that the photodiode cannot respond to the optical signal accurately, and thus does not produce an electrical signal that is 1:1, or a copy, of the optical signal. Instead, the input signal becomes elongated, as seen in Figure 2 at position 3 for the secondary arm.

This electrical signal from the photodiode is then used as an input to the electro-optic Mach-Zehnder modulator. The set-up of a Mach-Zehnder Modulator is shown below. It has an optical input, optical output, a DC bias, and an RF input. The optical pulse from the reference arm is the optical input. The modulator structure splits incoming optical energy 50/50 into two waveguides, one of which has a voltage applied to it which is the RF input from the photodiode.

Figure 3: MZM Structure. Shows a basic top-view representation of an MZM. The optical input is split into two arms, one of which is under a DC bias and is driven by an input RF signal. When the signals are recombined at the Y-junction, any differences in phase as well as how much the pulses are overlapped will determine the amplitude modulation.

When the RF input is applied to an arm of the modulator, this electric field changes the refractive index minutely. This change in refractive index means the light will travel either slower or faster through one of the arms of the device. These optical signals are recombined at the end of the device, where their differences in phase modulates the amplitude of the final optical signal. This is what we see at point 4. This recombination is where the pulse overlapping occurs, giving us the final output of the FREG. This overall process within the FREG is repeated for many different time delays, as seen in Figure 4b, so that we can build a spectrogram similar to the one seen in Figure 5a.

Figure 4a (Left): 2D Spectrum Example. Shows an example of what a pulse spectrum would look like. This is necessary for reference in conjunction with Figure 4b, as this shows how the spectrums are compiled to create a spectrogram.

Figure 4b (Right): 3D Spectrogram Example. Shows an example of what the spectrogram would look in 3-D, rather than the 2-D representation (such as Figure 4a). We see that each of the output spectrums created by varying the time delay are compiled to create a spectrogram.

Moving onto Figure 5a and 5b, we can finally answer the question: Why is it called Frequency-Resolved Electrical Gating? This term can be broken down into two parts. The "Electrical Gating" was seen in the last paragraph, where the time-delayed secondary arm's electrical signal modulated the optical signal from the reference arm. This is called gating because an output is only produced when the pulses are overlapping, i.e. the optical signal cannot pass unless the gating signal allows it to. This mechanism is produced in part by how the modulator is biased, which will be discussed in Section 6.1. The "Frequency-Resolved" portion of the term "FREG" refers to this technique's usage of a spectrogram to characterize the input. Because these pulses are too fast to be measured with a typical electrical detector, we instead take "snapshots" or probes of the input at various positions in time. This FREG output pulse is then fed into a spectrum analyzer, which breaks down the frequency components or wavelengths which compose the signal. This deconstruction of the signal occurs via measuring the power of the constituent wavelengths in the signal, then mapping it in a power-wavelength spectrum. A spectrogram is merely a collection of spectrums, at differing time delays. An example of a spectrogram is shown in Figure 5a. This "frequency-domain" spectrogram can be deconvolved utilizing a blind deconvolution algorithm to obtain the desired pulse information. Thus, the term "frequency-resolved" extends from the fact that we are using the frequency contents of the signal to resolve, or conclude, the pulse information.

Figure 5a: 2D Spectrogram Example. Shows an example of a 2D spectrogram. These spectrograms will be the output from the spectrum analyzer and the input into the deconvolution algorithm. [3]

Figure 5b: Retrieved Pulse Phase and Amplitude. Shows an example of the retrieved pulse and phase information from a spectrogram. Ideally, our GUI will return a similar result. The dashed red line shows the measured intensity, dashed green shows the measured phase, and the magenta and blue are the respective modelled values. [3]

To reiterate, the spectrogram measured by the OSA is a measurement produced in the frequency domain. This is important, as the time-frequency relationship is the crux of what makes spectrographic techniques such as FROG and FREG so successful. We know that the time-frequency relationship for signals is inverse, meaning that signals which are short in duration (time-domain) are composed of a wide range of frequencies or are "spectrally broad" in the frequency domain, and vice-versa. Due to the ultra-short nature of the pulses used, material dispersion effects have a strong effect on pulse propagation. Dispersion is a phenomena where different wavelengths experience different velocities when propagating through a material [25]. This is because refractive index is inherently dependent on wavelength. Thus, the large span of frequencies which compose an ultra-short pulse are affected differently in terms of propagation speed, causing pulse broadening. This ties back to characterizing these optical pulses in duration and phase, as pulse broadening due to dispersion threatens the signal integrity and limits the bandwidth of data transmission systems. Once a pulse is characterized, measures can be taken to counteract these dispersion effects.

The spectrogram can be used to determine the desired optical pulse properties via blind deconvolution. One of the biggest difficulties in this set-up is that not only is the input pulse not known, but the system transfer function is also unknown. This is the type of problem blind deconvolution aims to solve. A property of linear shift invariant (LSI) systems is that if two transfer functions amongst the input, impulse response/ system and output are known, the other transfer function can be found or characterized. Another relevant property is that convolution in the time domain becomes multiplication in the frequency domain. We also know that the Fourier transform transforms a function in time into a function in frequency. Thus, typically, cumulatively we could use these properties to easily solve for either the input, output or impulse response of a system. However, as we do not know both the input and the system transfer function, we must use a more complicated algorithm to decipher the input. Blind deconvolution utilizes educated assumptions about the system's input and transfer function to recreate the output function produced from the

system. These assumptions are then iterated until the guessed input and system transfer function match the original spectrogram. This complex algorithm will be discussed further in Section 3.3.3.

The last relevant portion of this system is the electronics which connectorize all the various components and sub-systems. The objectives for the electronics include communication to the TDL, supplying power, and controlling the grating. The overall cyclical flow of the communication within the system is as follows: A user on the PC wants to start a measurement, they enter in the scan information and press a button on the GUI to begin the scan, this sends a command through the MCU to the TDL, telling it to go to the first scan position. The motorized TDL should be fast, as the maximum possible latency of the TDL is ~5 seconds. Once the TDL position is set, the MCU must then send signals to rotate the diffraction grating such that we can begin creating a spectrum of the output signal. Since the system is manual, the user will need to capture the spectrum on the oscilloscope and send it to the PC. Once this process is complete, the user can press a button on the GUI to increment the TDL and repeat the process.

Communication between the PC and TDL is necessary, such that the PC knows the delay that the delay line is set to, so it can accurately assemble the spectrogram. The PC will be receiving the pre-made spectrum of the FREG output pulse from the oscilloscope, but this spectrum does not contain the time-delay information, which is why we require the communication link. Additionally, the spectrums obtained by the oscilloscope will require information about which wavelengths it is measuring to ensure the spectrogram mapping is accurate. The wavelength output by the OSA correlates with the degree of rotation of the grating, which is a relation we can precharacterize. Finally, the supplying of power and operating voltages to devices such as the two photodiodes and the diffraction grating's motor is desirable so we can limit the number of external connections the system has; however, it is to be determined what is practical in this regard.

To conclude the background, we find that the FREG is an elaborate system, with many factors to account for. However, this complexity comes with the powerful ability to characterize low-energy ultrashort input pulse trains.

#### 2.3 Project Goals

#### 2.3.1 Basic Goals

Basic goals are those which must be completed to create the simplest version of the FREG. Many of these are practically essential for the device to be functional.

- Create an apparatus to characterize low energy, optical pulses

- Have a GUI, which displays the results of the deconvolution algorithm and allows the user to save the results

- Make the system setup simple for the user

- Program microcontroller for the FREG

- Make FREG algorithm for the computer connected to the device

- Create PCB for external power delivery integration for the Mach-Zehnder Modulator

#### 2.3.2 Advanced Goals

Advanced goals are the immediate possible improvements to make once the basic project goals are completed.

- Be able to resolve and characterize pico-second pulses

- Have custom housing for the apparatus

- Have microcontroller software to decrease the amount of time it takes to create spectrogram from the pulse input

- Create additional features to FREG to include pulse data export to multiple file types

#### 2.3.3 Stretch Goals

Stretch goals are unlikely to be completed unless surprising significant advances are made quickly during project development. These are ideal changes to make if given the support of a company and given additional time to complete the project.

- Add an autocollimator to the setup for easy for easy free space to fiber transition

- Be able to resolve and characterize pulses on the order of around 100 femtoseconds

- Have a custom spectrum analyzer for the system

- Expand the GUI to be customizable to the user to include dark mode, color customization, and window size changes

## 2.4 Objectives

Objectives are actions that can be taken to achieve goals, they specifically tell us how we will accomplish our goals.

- Design fiber connection lengths to minimize dispersion

- Design beam splitter power ratio to bias the EOM with the minimum amount of power necessary

- Design the pulse overlapping between the two branches of the system to produce accurate spectrograms

- Design the amount of gating which is needed to resolve the optical pulses

- Design a grating for the optical spectrum analyzer which has a high spectral resolution and the desired wavelength of 1550 nm.

- Design the photodetection setup for the OSA such that these low-energy optical signals can be captured and processed to produce a spectrogram

- Create a program which produces accurate spectrograms

- Design and build an autocollimator

- Program a deconvolution algorithm to extract pulse duration and phase information from the spectrogram

- Develop a PCB to time-synchronize the OSA and gating mechanism

- Develop a PCB to handle power distribution to components

- 3D model and build the desired custom housing

Figure 6: System Overview. Blue lines indicate electrical connections; red lines indicate optical signals.

## 2.5 Engineering Specifications

| Table 1: Engineering Specifications |                        |                                                                                                                               |  |  |

|-------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Component                           | Parameter              | Specification                                                                                                                 |  |  |

| FREG FPD, MZM,<br>OSA               | Target Wavelength      | 1550 nm                                                                                                                       |  |  |

| MZM, FREG FPD                       | Desired Bandwidth      | 40 – 50 GHz                                                                                                                   |  |  |

| OSA PD                              | Sensitivity            | > -60dBm                                                                                                                      |  |  |

| FREG FPD                            | Single Mode Operation  | K connector: < 40 GHz<br>V connector: < 65 GHz<br>GPPO connector: <65 GHz                                                     |  |  |

| OSA                                 | Measurement Speed      | < 10 Minutes                                                                                                                  |  |  |

| OSA                                 | Spectral Resolution    | 0.1 - 0.5 nm                                                                                                                  |  |  |

| OSA                                 | Spectral Bandwidth     | 1515 nm – 1585 nm                                                                                                             |  |  |

| Housing                             | Ease of Handling       | Portable, Self-Contained, Accessible                                                                                          |  |  |

| System                              | Significant PCB Design | 4"X4" MSP430F6659 Microcontroller Programming cable LED: 330Ohms 2-10KOhms 10uF/16V capacitor 11.0592 MHz crystal Push button |  |  |

# 2.6 Block Diagrams

## 2.6.1 Hardware Block Diagram

Figure 7: Overall Block Diagram.

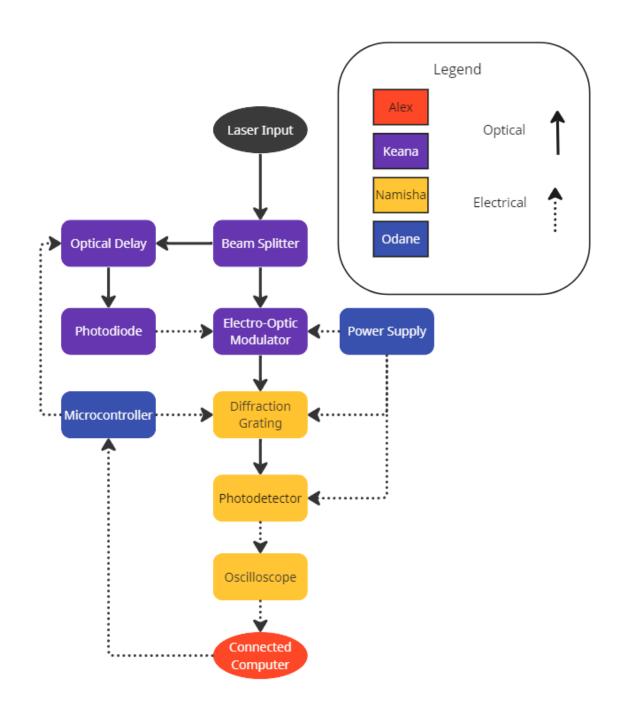

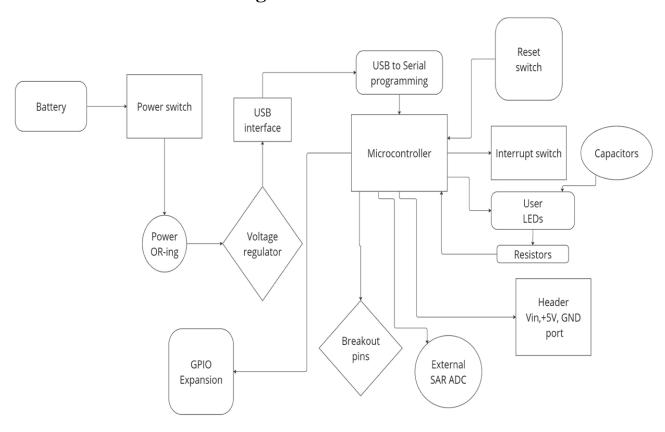

## 2.6.2 Electronics Block Diagram

Figure 8: Electronics Block Diagram.

## 2.6.3 Software Block Diagram

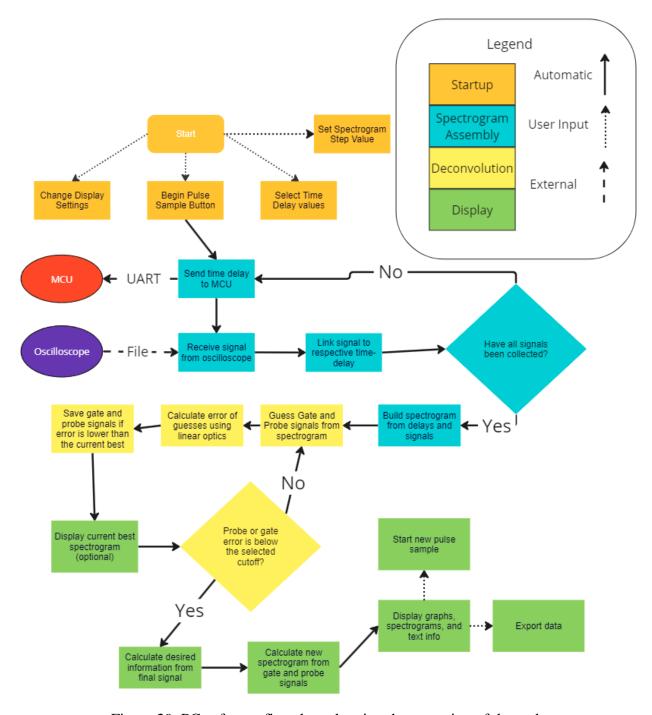

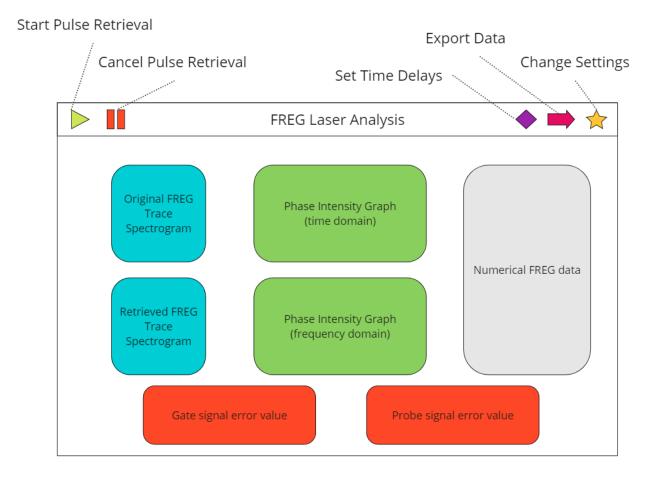

Figure 9: Software Block Diagram.

## 2.7 House of Quality

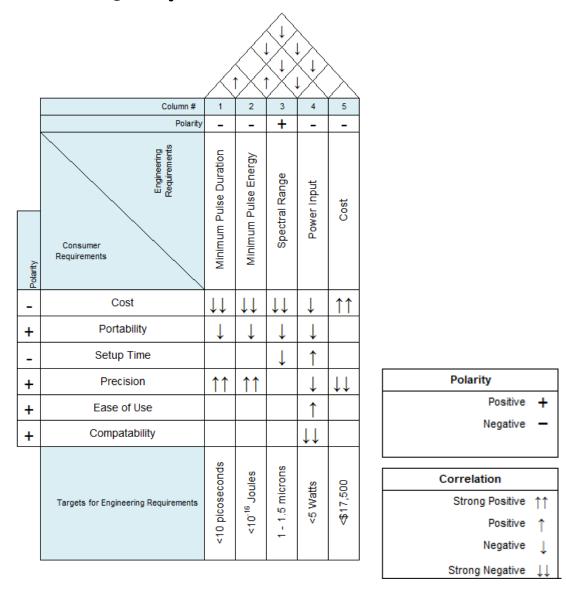

Figure 10: House of Quality for the FREG device.

### 2.7.1 House of Quality Description

The house of quality indicates that the desired outcomes of reducing the minimum possible pulse duration measurable and the minimum pulse energy measurable will decrease with cost. This means that more money will need to be spent to reach the main goal of measuring pulses with a duration of <10 picoseconds. Additionally, larger equipment has the ability to measure shorter pulses with a larger spectral range, so portability becomes more difficult as these requirements are met. Precision is the final consumer requirement with significant relation to the engineering requirements: improving the minimum pulse duration and pulse energy makes the device more precise.

The ease of use, compatibility, and setup time are more singular. The ease of use and compatibility are tied to the power input requirement due to the power input port of the FREG. If USB is used, the power input will be lower than other ports but the compatibility with computers will be higher. Using a more common cable makes the device easier to use, as a commonly used computer can be connected to the device and used rather than needing to find a computer and install drivers for a port that is not commonly used.

The roof of the house of quality shows the relationship between the engineering requirements. The minimum pulse duration has positive correlation with the minimum pulse power, as a faster modulator and photodiode will decrease the minimum values of both. However, reducing power input and cost will reduce the maximum speed of the modulator and photodiode. As minimum pulse energy decreases, the cost and power input increase for the same reasons as the pulse duration. Lastly, the spectral range decreases as cost and power decrease.

## **Chapter 3 Research**

# 3.1 Existing Similar Projects, Products and Relevant Technologies

The FREG has no commercially available alternatives. This is due to its relatively niche application and its configuration. Thus, there are no similar products to the system we will be building. However, there are similar projects in terms of adjacent research papers and researchers who have built systems similar to FREG. These papers will be discussed as a related work to our own work.; Specifically, we will be referencing the work of our advisor, who has built this system previously. An interesting note on the term "FREG", is that the term was concocted by researchers who were inspired by the FROG and utilized its configuration for use in the microwave domain [4]. Our use of the term returns the application to the optical domain.

#### 3.1.1 FROG

Related works to our project mainly concern the FROG and TADPOLE, the original proposal of the FREG, and more recent works utilizing the FREG. The FROG was first proposed in 1991, with a review article in 1997 solidifying its credibility as a measurement tool. The review article, "Measuring ultrashort laser pulses in the time-frequency domain using frequency-resolved optical gating", compares several beam geometries which are each a different FROG configuration and reports the performance of the pulse retrieval from each method. As previously mentioned, FROG requires non-linear optical pulse mixing, which is inherently high-power, and does not meet our requirement of an apparatus to measure low-energy pulses. A difference between the FREG and FROG besides their set-ups is that the spectrogram of a FROG is symmetrical due to the FROG set-up. This means that the deconvolution algorithm of the FROG likely assumes symmetry in the spectrograms, and this will need to be accounted for in our code, which will reference the original FROG code [5].

#### 3.1.2 TADPOLE

A system called "TADPOLE" is mentioned in the FROG review article [6] for the measurement of weak or complex pulses, which is applicable to our case. The difference between

TADPOLE and FROG is that TADPOLE combines FROG and spectral interferometry to achieve more sensitive measurements. TADPOLE sums the spectrum of two pulses, the exciting pulse and the resultant pulse, to retrieve the pulse information. Specifically, this set-up measures the strong exciting pulse to the laser source using FROG, and then uses spectrometry to deduce the weaker target pulse we are trying to characterize. This works due to the principle that any ultrashort pulse will require a high-energy input pulse to excite a non-linear medium. This means that weak pulses will always be accompanied by a high-energy exciting pulse. This is different from the FROG and FREG, which both utilize measurements of the spectrum at various time delays to extract the pulse information, as the TADPOLE only requires a single measurement of the spectrum to retrieve the desired information. However, it is not always possible to measure the exciting pulse to the laser source, which is one of the reasons why we choose to create a FREG over the TADPOLE [6].

#### 3.1.3 SEA TADPOLE

Another version of the TADPOLE is the SEA TADPOLE, which uses spatial fringes instead of spectral fringes. SEA is abbreviated to mean Spatially Encoded Arrangement, while TADPOLE is the same abbreviation as stated in the previous paragraphs. This system improved the spectral resolution and gained a factor of around 5. The SEA TADPOLE was also used to measure complex pulses to achieve spectral super-resolution. This was done by measuring the spectral phase of a 14-picosecond double pulse that was generated by a Michelson interferometer. This technique is able to determine the pulse intensity and phase for long pulses that have a finer spectral structure. The flaw this SEA TADPOLE system has however is the extreme sensitivity it has due to its linear-optical method. Only a small portion of the pulse beam is needed to be coupled into the device along with polarization maintaining fibers being used to keep identical polarizations. Our system would not require the polarization maintaining fibers, however it does need to be very sensitive to capture the pulses when capturing the phases. [5]

#### **3.1.4 SPIDER**

There seems to be a nature trend going on because the next technique that relates to the FROG is the SPIDER, which stands for the Spectral Phase Interferometry for Direct Electric field Reconstruction. This principle is performed by combining interferometry and spectral shearing in order to retrieve the phase information. This is done without having the need to use any iterative algorithm. This method has shown higher efficiency in terms of having a faster technique to reconstruct the temporal profile of a pulse. This was shown to be beneficial for faster optimization of pulses from a femtosecond laser. These techniques also demonstrated more enhanced measurement speed and it is also able to characterize individual optical pulses. This nonlinear implementation retrieves the spectral phase by collecting and scanning the fringe pattern from the replicated pulse and the tested pulse. These were collected after going through the interferogram. A group delay is an important feature in SPIDER because once it is integrated with the frequency then the spectral phase is collected and then a Fourier transform is performed. The Fourier transform is calculated with the power spectrum to the reconstruction of the time-domain image of the electric field of the tested pulse. This relates to the FREG system as we are implementing a time delay to capture the phase of the femtosecond pulse phases by combining it with a high frequency bandwidth from a photodiode. The purpose is to also reconstruct the spectrograms from these pulses, however rather than creating an estimated image, the system is to capture the pulse durations. [7]

#### 3.1.5 FREG First Configuration

The first instance of a FREG was conducted in 2002 by Christopher Dorrer and Inuk Kang [2], in the letter "Simultaneous temporal characterization of telecommunication optical pulses and modulators by use of spectrograms". They achieved a fast bit rate of around 40 Gbits per second and low peak power that was less than 1 mW. This method was also described to not rely on the need for nonlinear optics and the system is extremely sensitive, hence why it has been adopted for the purpose of low-energy characterization of 1550-nm sources for telecommunications. The main difference between this paper and our intended set-up is a higher desired operating frequency due to a shorter input pulse width, and instead of using an electro-absorption modulator as the gate, we are using an electro-optic modulator. Their set-up also tests whether amplification, broadening of the spectrum using non-linear self-phase modulation, and then linear recompression of the signal affects the retrieved pulse. They also attenuate the input signal from 0.1 mW to 0.1 µW to see how sensitive the FREG is. In both cases, the retrieved pulses are as expected, with minimal error. The acquisition time of the desired pulse information for this system was 3 minutes. However, as speed of retrieval is not one of the main priorities for our customer, we will prioritize the accuracy of the system first. However, it would be favorable to improve on this acquisition time. Thus overall, this letter not only was the first demonstration of a FREG system, but it also demonstrated robustness in operation and defines some design parameters which we utilized for our system.

For a more contemporary instance of FREG implementation, we have been referencing work by our advisor, Dr. Andrea Redondo-Blanco. Specifically, her paper called "Controlling free-carrier temporal effects in silicon by dispersion engineering", where she details the FREG set-up which she uses for several different research papers which concern silicon photonics and solitons. In this paper, the FREG set-up is more like the version we are making when compared to the original proposal paper, with the major difference being that the DUT is after the beam splitter rather than before it. This change does not affect the overall operation of the system, as the spectrogram can still be obtained in a similar manner. Because the set-up used in this paper is more like ours than the original proposal, we utilized it as a basis for our design. The main difference between our system and this FREG is that we aim to improve the system's minimum pulse duration, which can be measured.

As a starting point for the software, we will use code provided by the Trebino group at Georgia Tech [5], which we shall consider a related work. This code operates using a deconvolution algorithm to produce the intensity and phase by time and frequency as described above. The FROG algorithm will be replaced with one suitable for the FREG for the same purpose of measuring the characteristics of a laser pulse. MATLAB will be used to develop this algorithm due to its large libraries with math functions and due to the FROG code existing on MATLAB. The algorithm can then be included in a more complete program with a proper GUI using a language such as Java, potentially using integrated MATLAB functions.

### 3.2 Hardware Part Selection

#### **3.2.1 FREG Components**

For a FREG, the vital components include a photodiode, an electro-optic modulator, and a time delay line. In the following section, we will begin with an explanation of the component's function within the system, and an explanation of relevant functionality. We will then discuss the types of components which fall under the branch of the term used, why other variations of these components were not selected, and we will discuss the relevant qualities for the specific type of device we are looking for and how these qualities can affect the output. Finally, we will aggregate this information to select the final components for the project.

#### 3.2.1.1 The Modulator

The modulator is necessary to gate the pulse at different points during the pulse duration such that we can characterize the input pulse train via its impulse response. Specifically, it utilizes the output from the photodiode to modulate the input optical signal from the reference arm. This is because the signal passes through the TDL and into the photodiode and the length of the time delay or optical path length determines how much the input and delayed signals overlap within the modulator. There are a few types of basic modulators: intensity, phase, and both intensity and phase (called "I/Q").

From the general scheme of the FREG, due to our desire to measure the pulse duration and phase, we can whittle down the desired characteristics of the modulator. The set-up of the FREG is that a signal is convolved with a time-delayed version of itself to create a spectrogram. The pulse duration of an input signal is determined by multiple intensity measurements from the system using the input pulse train; however, these measurements are normalized due to the consistent "impulse" coming from the phase-delayed arm of the modulator. Thus, intensity modulation will allow us to create slices of the spectrogram via convolving the input signal at multiple points in time. We see that the spectrogram produced by the FREG is a measure of intensity, wavelength, and time.; Thus, we know that we must use an intensity modulator. Additionally, because we aim to measure pulse duration and phase, we know that using a phase modulator would only complicate extraction of the pulse phase information. For this particular spectrographic technique, we do not obtain any useful information from phase modulation, and thus, only utilize intensity modulation to extract the pulse characteristics.

There are several types of intensity modulation: Acousto-optic modulators (AOMs), Electro-optic modulators (EOMs), Electro-absorption modulators (EAOMs), semiconductoroptical-amplifier-based modulators (SOAMs), and liquid crystal modulators (LCMs) [8]. Acoustooptic modulators do not have the desired bandwidth that is expected of a system which will characterize ultrafast optical pulses.; AOMs have a <10 GHz operating bandwidth, whereas the device described in this paper has a >40 GHz bandwidth. Additionally, these bandwidths are generally "bandpass" rather than "lowpass" [8]. This makes the device operation undesirable for the FREG setup, as the characterization apparatus requires a relatively broadband response. LCMs are similarly severely limited in modulation bandwidth, due to their switching relying on the changing of its molecules' orientation, which takes milliseconds [9]. SOAMs have a better extinction ratio than AOMs and EOMs, however, the introduction of amplifier noise makes them unideal for a sensitive system. This is because noise has the potential to overhaul the signal we wish to measure because these signals are very low in energy. Additionally, they have a larger form factor, are less available, and are more costly than the typical EOM. EAOMs were used in the original proposal of the FREG [2]. EAOMs tend to have a higher modulation bandwidth and lower required drive voltage than EOMs, both of which are factors which are favorable in this setup. However, through our research we have found that these devices, in our desired range of 40-50 GHz, are not as readily commercially available when compared to EOMs. This could likely be due to their small form-factor which makes them more suitable for monolithic chip integration [10]. Additionally, they experience more chirp than EOMs and the amount of chirp changes with voltage [11].

With regards to EOMs, there are two main configurations: Pockel's Cell (PC) and Mach-Zehnder (MZ). The Pockel's Cell's utilizes polarization, whereas the Mach-Zehnder configuration is based on interferometry to produce an intensity modulation [10]. PC modulators utilize a bulk anisotropic crystal in a (typically) cylindrical housing, wedged between two electrodes, to modulate incoming optical signals. These devices impose a phase delay on incident optical signals when a voltage is applied to the crystal through the electrodes. Specifically, an applied voltage alters the polarization state of incident light. Thus, to use a PC for amplitude modulation, the PC must have a polarizer placed both in front of the PC and after it. This allows the modified polarization to be converted into a modulation in light intensity. This is because polarizers block light polarizations which don't align with their designed polarization state.

Pockel's cell modulators have a significantly lower bandwidth (<10 GHz) and are much bulkier in comparison to MZ modulators. In addition, a majority of Pockel's Cells are for free-space optics. This is important because we require the modulator to be fiber connectorized due to the low energy optical pulses used in the FREG. This is because waveguiding (such as optical fiber) will reduce input energy losses better than free space propagation especially if the input optical energy is uncollimated. [11]

The Mach-Zehnder modulator utilizes the two-arm interference structure of Mach-Zehnder interferometers with one important change: The optical path length (OPL) change and subsequent phase shift is induced in the device via the electro-optic effect rather than manually via mirror movement. This allows the device to be integrated and fiber connectorized rather than free space, which again reduces the optical energy losses. The linear electro-optic effect (also known as the Pockel's effect) [12] is when a voltage change induces a refractive index change in materials with a specific crystal structure. Specifically, the linear electro-optic effect shows a relation between the material polarization and the square of the applied external field [13]. Lithium Niobate (LiNbO3) is one of these materials. Lithium Niobate (LN) is a very common material for photonic devices due to its strong electro-optic effect, and in this case is the material used for the MZ modulator. LN has a negative uniaxial crystalline structure, which can help in derivations of the linear electro-optic coefficients for the material. The Pockel's effect in LN can be quantized via the associated electro-optic coefficients, shown below:

Table 2: Pockel's Effect or Linear Electro-Optic Coefficients and Refractive Indices for Lithium Niobate at 1550 nm.

| r13 (pm/V) | r51 (pm/V) | r33 (pm/V) | r22 (pm/V) | no    | ne    |

|------------|------------|------------|------------|-------|-------|

| 8.6        | 28         | 30.8       | 3.4        | 2.210 | 2.138 |

Note that r42=r51, r22=r-12=r-61, r12=r23, where the electro-optic coefficients are measured in picometers per volt. These coefficients refer to the change in optical path length per voltage due to an applied electric field. These coefficients describe the directions in the lattice

geometry which contribute to this change in refractive index and their magnitude of influence. "no" and "ne" denote the ordinary and extraordinary refractive indices respectively.

The device structure of a MZM consists of the previously mentioned constituents: A 50/50 splitter, two optical waveguides in bulk lithium niobate (LN), RF waveguides and a 50/50 combiner. This structure can be seen in Figure 3 The 50/50 splitter splits the optical input in half, guiding it into each of the LN waveguides. The LN optical waveguides have a structure similar to optical fiber, where there is a higher refractive index trapping light within a medium of slightly lower refractive index. This trapping is based on a phenomenon called total internal reflection (TIR). To achieve this designed difference in refractive index for TIR of the incident light through the waveguide, Titanium doping is commonly utilized which increases the refractive index of the LN.

Thus, the light in the MZM is guided via total internal reflection, where the dimension of the doped waveguide determines the propagating light's mode and the effective refractive index it experiences. The RF waveguide introduces a modulating signal which changes the refractive index of either one or both arms of the modulator, depending on the modulator configuration. The change in refractive index is precisely due to the movement of charge carriers within the MZM, due to the applied voltage. The refractive index change, as previously mentioned, is due to the Pockel's effect, and is realized as a change in optical path length for the optical signal.

Both the DC bias voltage and RF bias of the modulator contribute to a relative phase difference between the two arms of the MZM. When these optical signals with a difference in phase are recombined, the output is intensity modulated accordingly. This recombination of light causing the intensity modulation is why we refer to this method as an interferometric-based modulation, compared to the polarization-dependent modulation of the PC. However, some properties of the polarization within the material do play a part in the overall functionality of this device.

Typical characteristics of the MZM we used to determine which device would be best for this set-up included the electro-optic bandwidth / S21 response, wavelength range, RF impedance matching, driving voltage, insertion loss, extinction ratio, electrical connector type, and optical connector type.

The electro-optic (EO) bandwidth tells us the range of operation for the modulator. The electro-optic bandwidth of a modulator is limited by the shortest pulse which the device material can accurately respond to. This can be thought of similarly to slew-rates in op-amps, if the input changes faster than the device is able to respond, the device will not have an output which is as sharp in slope as the input. Eventually, if the device's response rate is exceeded too much, the input pulse may not even be detectable by the device. Thus, the electro-optic response of a modulator is a measure of a device's ability to respond to changes in an applied electric field. This applied electric field causes a change in carrier concentration within the device, which changes the refractive index, as previously mentioned.

When looking at graphs of EO bandwidth, we see that "S21" is used to describe the response. S21 refers to a signal emerging from port 2 of a device due to a stimulus from port 1 of a device, and thus represents transmission or forward power gain. This is important because we wish to maximize the response of this system and be able to modulate short optical pulses (picosecond- 100 femtosecond), which require 10+ GHz of bandwidth, at least. Generally, devices

were advertised utilizing their -3 dB and - 6 dB bandwidths. Ideally, for this system we were looking for -3 dB bandwidths of 35 GHz or larger. This generally guarantees that the device will operate up to 50 GHz as typically the roll-off of the frequency response for these MZMs are not steep.

The wavelength range is vital because we want the modulator to be able to modulate optical signals with the input wavelength we desire. This wavelength is 1550 nm and is in the C band, which is a telecommunications standard operating wavelength range which spans from 1530 – 1565 nm [14]. Modern optical fibers have the lowest losses in this wavelength range which is why a wavelength of 1550 nm has become a standard operating wavelength for optical communications.

Impedance matching is important once you reach the radio frequency, or RF, range of electrical signals. At high frequencies, electrical signals behave similarly to optical signals. For example, they experience reflections, dielectrics experience standing RF waves, they have a forwards and backwards transmission, etc. Light experiences some fraction of reflection and transmission at an interface or change in refractive index. RF signals also experience reflection and transmission at interfaces, where rather than comparing the refractive index, we look more to the property of characteristic impedance, to identify how the RF wave will be reflected and transmitted through the coaxial connection. Thus, we prefer for the impedance between RF transmission lines or waveguides to be matched to minimize losses due to reflections away from the desired signal direction.

The driving voltage of an MZM is what typically controls the phase shift in each of the arms of the device. As previously mentioned with the electro-optic effect, it requires an applied electric field to change the refractive index, and thus the OPL, of light going through a material with strong electro-optic properties. The driving voltage is typically externally applied with the use of a modulator driver. However, due to a combination of the type of modulator we have chosen and the configuration of the FREG, this is unnecessary. There are two types of MZMs when it comes to the type of drive: single drive and dual drive. A single drive means that only one of the arms of the modulator is being biased with a voltage. Thus, because we have chosen a single drive, and have the photodiode linked up to the MZM, the photodiode replaces the need for a modulator driver.

Furthermore, single drive means that the full driving voltage must be applied to the arm to get the maximum extinction ratio [15]. The driving voltage or wave voltage is often denoted as  $V\pi$  and refers to it being the voltage required to induce a phase shift of  $\pi$  in the output signal. In dual drive, both arms are being driven, and only half of the driving voltage needs to be applied to each to achieve the maximum extinction ratio. By making these applied driving voltages equal in amplitude and opposite in sign, chirp can be eliminated from the modulator. Thus, we see that dual-drive is preferred over single-drive modulators, as chirp is an undesirable quality.

Elimination of chirp in the FREG is important for preserving the integrity of the measured optical pulse information, specifically the measured phase information. This is because phase shows how the frequency components in a signal change over time, and chirp is either the increase or decrease of a signal's frequency over time. Chirp is often due to nonlinearities in a material or dispersion [16]. Chirp and the types of drives in MZ modulators link further to the types of device geometries and the crystal cuts within MZ modulators.

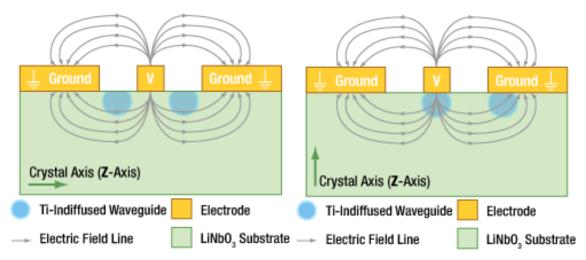

Due to biasing, dual drive MZMs are inherently symmetrical in structure which eliminates chirp. However, for single drive MZ modulators, there is the Z-cut configuration and an X-cut configuration, which each refer to the crystal cut of the MZM which subsequently creates the device's geometries. X-cut is preferable to Z-cut single drive MZM modulators because they are more symmetric and consequently chirp-free [17].

Figure 11: MZM Crystal Cuts. Shows the differences between the different single-drive MZM crystal-cut configurations. [17]

Insertion loss is a measure of the signal power loss in decibels when a signal travels into a given device. Due to the low-energy application of the FREG, we must be extremely cautious when factoring the signal losses. Losses in this set-up will likely be mainly attributed to insertion losses into various components and fiber propagation. Thus, these values must be taken into account to make sure that they do not exceed nor eclipse the desired signal strength.

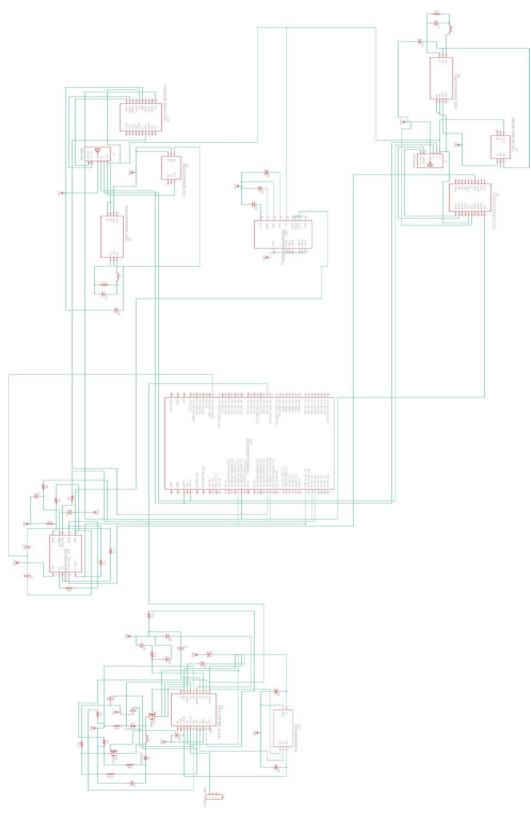

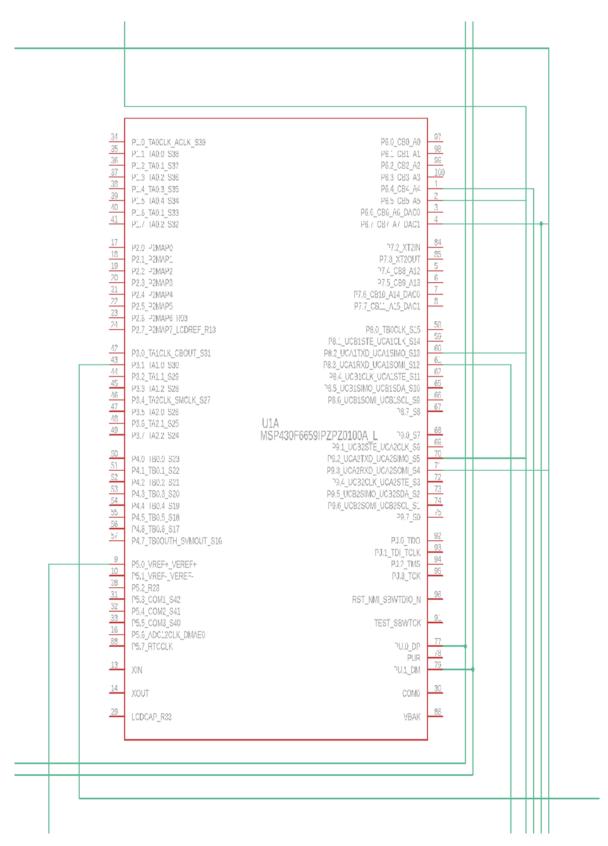

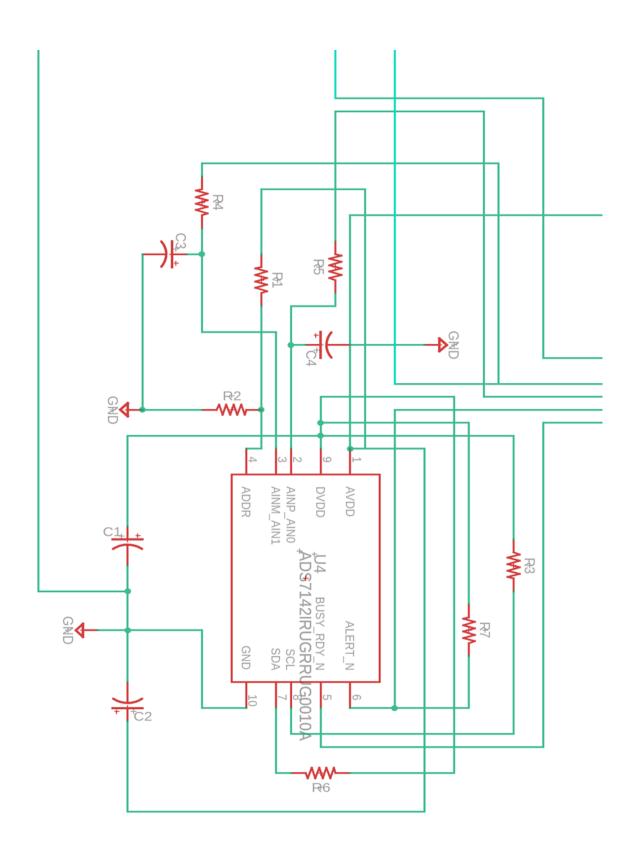

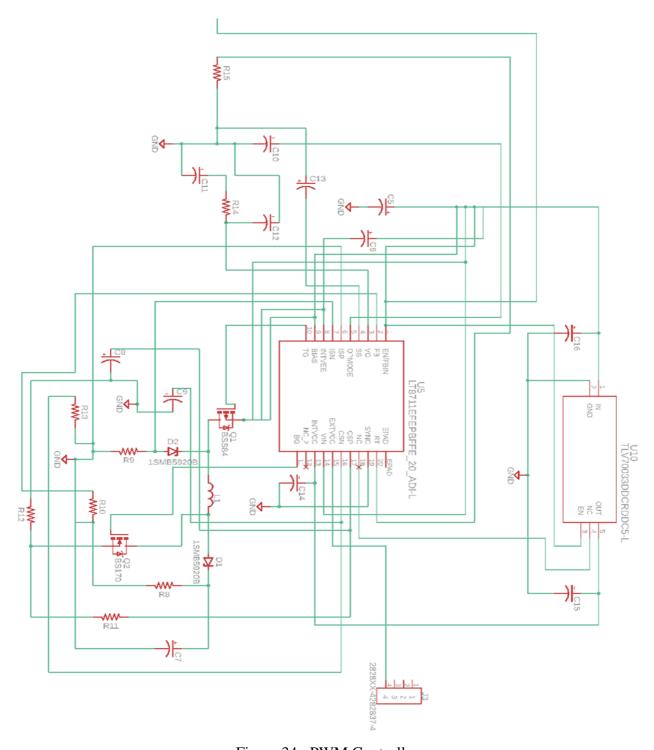

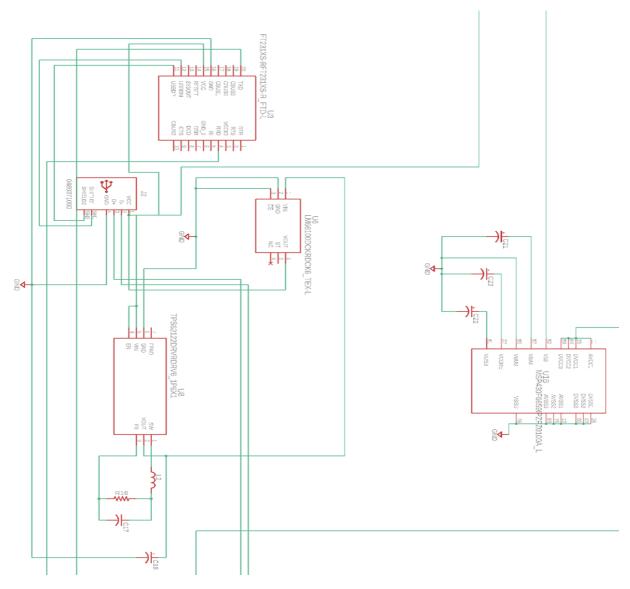

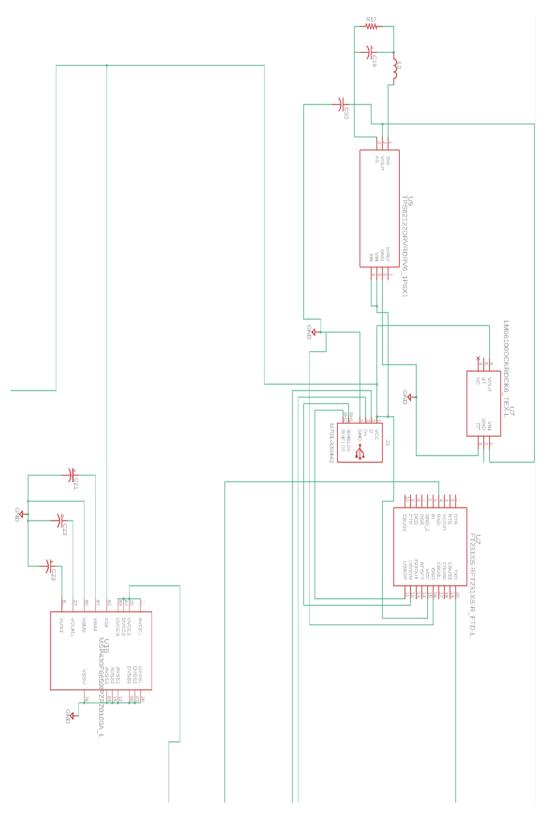

The extinction ratio is essentially the contrast, or maximum output to minimum output you can get out of a device. This extinction ratio relates to establishing the gating of the FREG. As previously mentioned, the extinction ratio must be designed for via the modulator biasing, specifically the DC biasing. In Section 6.1, we will discuss why we have biased the modulator the way we have and how we characterized the extinction ratios of our modulators. Overall, the larger the extinction ratio is, the better it is for the device operation.